ZYNQ开发实例之布局约束

本文共 739 字,大约阅读时间需要 2 分钟。

分享一例位置约束实例

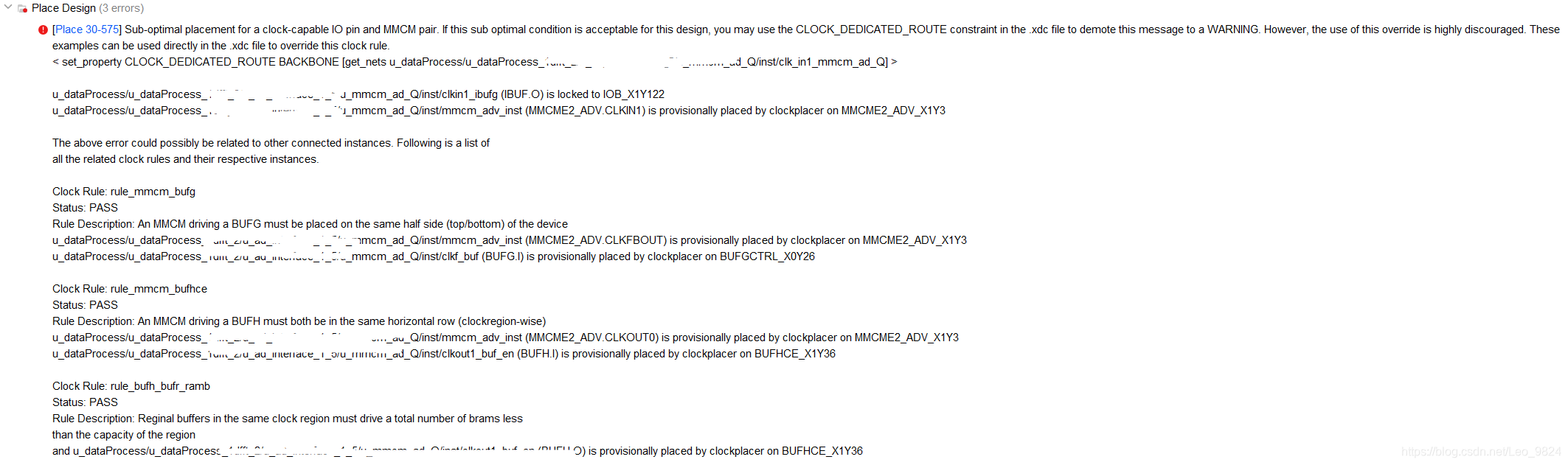

如下图所示,出现这个警告的意思是在一个bank中时钟管理器不够用需要到其他bank中找一个,但这不是最优的解决方案,如果要这么处理就需要在约束文件中进行约束

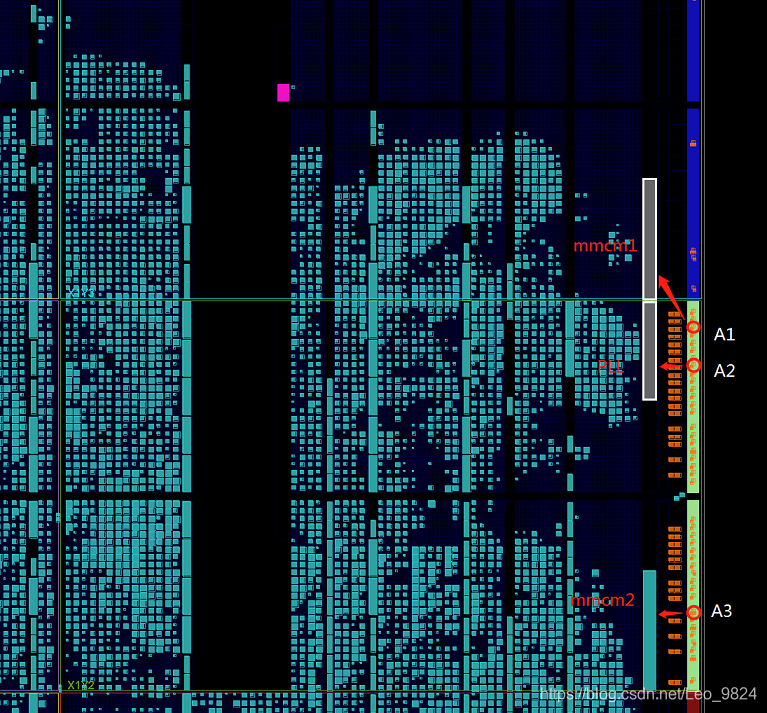

先分配一下IO对应的时钟管理器。A1分配mmcm1,A2分配PLL,A3分配mmcm2,如下图:

可以在属性中获取时钟管理器的坐标:

mmcm1的坐标是MMCME2_ADV_X1Y3 pll的坐标是PLLE2_ADV_X1Y2 mmcm2的坐标是MMCME2_ADV_X1Y2可以在Schematic中找到时钟管理器的网络路径:

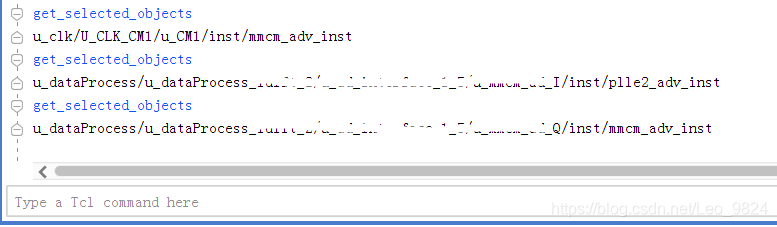

鼠标选中目标器件,在tcl中输入get_selected_objects命令就会打印出目标路径 约束:

约束: 消除警告

set_property CLOCK_DEDICATED_ROUTE BACKBONE [get_nets clk_9516]位置约束

set_property LOC MMCME2_ADV_X1Y3 [get_cells u_clk/U_CLK_CM1/u_CM1/inst/mmcm_adv_inst]位置约束

set_property LOC PLLE2_ADV_X1Y2 [get_cells u_dataProcess/u_dataProcess_1dfft_2/u_ad_interface_1_5/u_mmcm_ad_I/inst/plle2_adv_inst]位置约束

set_property LOC MMCME2_ADV_X1Y2 [get_cells u_dataProcess/u_dataProcess_1dfft_2/u_ad_interface_1_5/u_mmcm_ad_Q/inst/mmcm_adv_inst]转载地址:http://jzfiz.baihongyu.com/

你可能感兴趣的文章